Более сложным преобразователем информации являются схемы с памятью. Наличие памяти в схеме позволяет запоминать промежуточные состояния обработки и учитывать их значения в дальнейших преобразованиях. Выходные сигналы Y = (y1, y2, …, уm) в схемах данного типа формируются не только по совокупности входных сигналов

Х = (х1, х2, …, хn), но и по совокупности состояний схем памяти Q = (q1, q2, …, qk). При этом различают текущий дискретный момент времени t и последующий (t+1) момент времени:

Передача значения Q между моментами времени t и (t+1) осуществляется обычно с применением двухступенчатой памяти и синхронизирующих импульсов (СИ).

В качестве простейшего запоминающего элемента (ЗЭ) в современных ЭВМ используют триггеры. В связи с успешным применением микроэлектроники в схемах основных устройств ЭВМ (процессоров и оперативной памяти) исчезли в качестве запоминающихся элементов схемы, использующие остаточную намагниченность — ферритовые сердечники. Самая простейшая схема триггера может быть синтезирована по общим правилам.

Триггер – электронная схема, обладающая двумя устойчивыми состояниями 0 и 1. Переход из одного устойчивого состояния в другое происходит скачкообразно под воздействием управляющих сигналов. При этом также скачкообразно изменяется уровень напряжения на выходе триггера. Триггеры служат основой для построения регистров, счетчиков и других элементов, обладающих функцией хранения.

Триггеры можно классифицировать по различным признакам, например, так, как это показано на рисунке ниже. Структура триггера определяется в зависимости от элементной базы и таблицы переходов, которая является модификацией таблицы истинности.

Главной частью любого триггера является запоминающая ячейка (ЗЯ). Схема запоминающей ячейки на элементах «И-НЕ» представлена на рисунке:

Входной сигнал S (Set) служит для установки ЗЯ в состояние «1» (Q=1, ![]() ). Сигнал R (Reset) устанавливает ЗЯ в состояние «0» (Q=0,

). Сигнал R (Reset) устанавливает ЗЯ в состояние «0» (Q=0, ![]() ). Активными значениями для них являются сигналы низкого уровня.

). Активными значениями для них являются сигналы низкого уровня.

RS-триггеры

Рассмотрим таблицу переходов для асинхронного RS-триггера:

| Входы |

Состояние qt+1 |

|||

|

R |

S | 0 | 1 |

Режим |

|

0 |

0 | 0 | 1 |

Хранение |

|

1 |

0 | 0 | 0 |

Установка 0 |

| 0 | 1 | 1 | 1 |

Установка 1 |

| l | l | ? | ? |

Запрещенное состояние |

Содержание таблицы расшифровывается следующим образом. Элемент памяти может сохранять значение qt=0 или qt=1 в зависимости от установки ранее установленного состояния. При отсутствии входных сигналов на входах R и S (R =0 и S =0) значения qt+1 первой строке таблицы в точности повторяют значения qt. При поступлении сигнала R=l (сигнала установки «нуля») элемент независимо от своего состояния принимает значение, равное нулю, qt+1=0. Если же на вход S поступает сигнал установки «единицы» (S=1), то qt+1=1 независимо от предыдущего состояния qt. Одновременное поступление сигналов на входы R и S является запрещенной ситуацией, так как она может привести к непредсказуемому состоянию. В схемах формирования сигналов R и S должны быть предусмотрены блокировки, исключающие их совпадения, S=R=1.

Для таблицы переходовможет быть построена диаграмма Вейч:

В этой таблице знаком «~»отмечены запрещенные комбинации входных сигналов. Эти комбинации могут быть использованы для упрощения логических зависимостей. Логическая зависимость, описывающая работу элемента памяти, принимает вид:

Это уравнение получено путем эквивалентных преобразований. Добавление в него комбинаций, соответствующих запрещенным ситуациям и помеченных знаком «~», т.е.

![]()

позволяет еще больше упростить уравнение триггера:

![]()

Для реализации полученной зависимости в базисе «И-НЕ» применим правило де Моргана и получим функцию

![]()

По данной зависимости можно построить схему элемента памяти — асинхронного RS-тригера. В этой схеме следует только соединить выход qt+1 со входом qt. На рисунке 3.9 эта связь отмечена штриховой линией.

а- схема; б — обозначение на принципиальных электрических схемах;

в — временная диаграмма

RS-триггер нашел широкое распространение в схемах ЭВМ. Одиночные триггеры этого типа часто используются в различных блоках управления. В асинхронных RS-триггерах имеется один существенный недостаток, обусловленный самой логикой их построения (см. таблицу 3.4), т.е. в них сигналы R и S должны быть разнесены во времени. Дополнение этого триггера комбинационными схемами синхронизации на входе и выходе позволяет получить триггеры с более сложной логикой работы: синхронные RS-триггеры, Т-, JK-, D- триггеры и целый ряд комбинированных RST-, JKRS-, DRS-триггеров.

Прописные буквы в названиях триггеров обозначают:

- R (Reset — сброс) — вход установки триггера в нулевое состояние Q=0;

- S (Set — установка) — вход установки триггера в единичное состояние Q=1;

- Т (Toggle — релаксатор) — счетный вход триггера;

- J (Jerk — внезапное включение) — вход установки JK-триггера в единичное состояние Q=1;

- К (Kill — внезапное выключение) — Q=0;

- D (Delay — задержка) — вход установки триггера в единичное или нулевое состояние на время, равное одному такту;

- С (Clock — часы) — вход синхронизирующих тактовых импульсов.

Триггер называется синхронным, если его таблица переходов хотя бы по одному управляющему входу реализуется под воздействием синхронизирующего сигнала. Обобщенная схема синхронного одноступенчатого триггера приведена на рисунке ниже:

Основу синхронного одноступенчатого триггера составляет рассмотренная выше запоминающая ячейка (элементы 1, 2). Комбинационная схема преобразует управляющие сигналы триггера, а также, для некоторых типов триггеров, сигналы Q и Q с выходов ЗЯ в сигналы S и R на входах запоминающей ячейки. Синхросигнал C разрешает передачу на входы элементов 1 и 2 таких значений сигналов S и R, которые устанавливают ЗЯ в то или иное состояние. Неактивное значение синхросигнала обеспечивает на входах запоминающей ячейки состояние управляющих сигналов S = R = 1, что соответствует для нее режиму хранения.

На следующем рисунке показаны схемы синхронного однотактного (а) и двухтактного (б) RS-триггеров.

а, б — варианты

Двухкаскадная схема RS-триггера нашла наиболее широкое применение для построения n-разрядных схем запоминания — всевозможных регистровых схем. Штриховыми линиями на схеме указаны дополнительные точки подключения сигналов установки и сброса.

Представленный на данном рисунке триггер имеет статическую синхронизацию, при которой управляющие сигналы активизируют входы S и R запоминающей ячейки во время высокого уровня сигнала на входе синхронизации. Его условно-графическое обозначение приведено на рисунке а). Условно-графические обозначения триггеров, использующих другие типы синхронизации, приведены на рисунках б), в), г) (на примере RS-триггера).

На рисункеб) представлено условно-графическое обозначение триггера со статической синхронизацией в случае, если активный уровень синхросигнала низкий. Условно-графические обозначения триггеров с динамической синхронизацией показаны на рисунке в), г). В первом случае изменение состояния триггера под воздействием поступивших управляющих сигналов происходит только в момент переключения синхронизирующего сигнала с низкого уровня на высокий, а во втором – при переключении с высокого на низкий уровень. При постоянном значении уровня синхросигнала состояние выхода триггера с динамической синхронизацией не меняется при любых изменениях управляющих сигналов на его входах.

а — статическая синхронизация; б — статическая инверсная синхронизация;

в — динамическая синхронизация передним фронтом синхросигнала;

г — динамическая синхронизация задним фронтом синхросигнала

Как отмечалось выше, синхронный триггер, помимо управляющих входов, воздействующих на его состояние при подаче сигнала синхронизации, может иметь входы, которые воздействуют на его состояние непосредственно. Обычно они используются для установки триггера в то или иное начальное состояние перед подачей последовательности синхросигналов.

Сигналы, поступающие по асинхронным входам S и R, подаются непосредственно на входы запоминающей ячейки, образованной элементами 1 и 2, минуя цепь, управляемую синхросигналом (элементы 1 и 2), и вызывают переключение запоминающей ячейки согласно таблице 3.4.

Триггеры некоторых типов используют значения выходного сигнала для формирования управляющих сигналов на входах запоминающей ячейки. Это может привести к непредсказуемой последовательности его переключений. При построении отдельных схем на основе триггеров, например, регистров сдвига, необходимо, чтобы значения выходных сигналов триггера не изменялись на то время, пока производится их запись и значения его выходных сигналов в другой триггер, но сам этот триггер должен воспринимать значения с выхода некоторой другой триггерной схемы. Эти, а также некоторые другие ситуации требуют особых подходов к организации триггера, основным из которых является создание двухступенчатых триггеров.

Двухступенчатый RS-триггер

Двухступенчатый RS-триггер строится на основе двух одноступенчатых триггеров с прямой статической синхронизацией. Информация в первую ступеньтриггера (элемент 1) заносится во время действия высокого уровня синхросигнала. После того как синхросигнал на входе принимает низкое значение, элемент 1 переходит в режим хранения, а значение высокого сигнала на выходе инвертора 3 обеспечивает запись состояния триггера 1 в триггер 2.

Т-триггер

На рисунке ниже приведена схема Т-триггера или иначе — триггера со счетным входом. При значении Т=0 триггер сохраняет свое ранее установленное состояние — режим хранения состояния, при Т=1 триггер переходит в противоположное состояние. Таблица переходов и диаграмма работы отражают динамику работы этого элемента.

а- функциональная; б — условное обозначение; в — временная диаграмма

Таблица переходов Т-триггера

|

Входные сигналы |

Состояние qt |

Режим |

|

| Xt | 0 |

1 |

|

| 0l | 01 | 10 |

Хранение Инверсия |

По таблице переходов можно получить логическую функцию, реализуемую Т-триггером:

Нетрудно видеть, что данная зависимость очень похожа на функцию, выведенную для одноразрядного комбинационного полусумматора.

JK-триггер

Наиболее сложным типом триггера является JK-триггер. Он, по существу, является объединением двухтактного RS- и Т-триггеров. Этому соответствует его таблица переходов.

Таблица переходов JK-триггера

|

Входные сигналы |

Состояние q | Режим | ||

| J | K | 0 | 1 | |

| 00

0 l |

l0

l l |

0l

0 0 |

10

l 0 |

Хранение Установка 0 Установка l Инверсия |

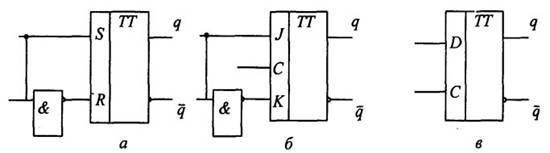

а — функциональная схема; б — условное обозначение

Следует отметить, что первая ступень представляет собой одноступенчатый триггер, реализующий заданную таблицу переходов, в то время как вторая ступень – это всегда одноступенчатый синхронный RS-триггер.

D-триггер

Динамический триггер D-триггер обычно строится на основе двухтактного RS- или JK-триггера. Он предназначается для хранения состояния (1 или 0) на один период тактовых импульсов (с задержкой на 1 такт).

Таблица переходов D-триггера

|

Входные сигналы |

Состояния q | Режим | |

|

D |

0 |

l |

|

| 0l | 01 | 01 |

Установка 0 Установка l |

a- функциональная схема на основе RS-триггера;

б- функциональная схема на основе JK-триггера;

в — условное обозначение

Все перечисленные элементы памяти позволяют хранить одну единицу информации – бит или одну двоичную цифру.